Chapter 1. Introduction 5

At a crossroad with mainframe technology, HPSSDL experimented with off-the-shelf RS/6000

machines interconnected by ESCON® Channel adapters and an ESCON Director. The

RS/6000 machines were repackaged as nodes and mounted in drawers, which were then

mounted with five drawers to a frame.

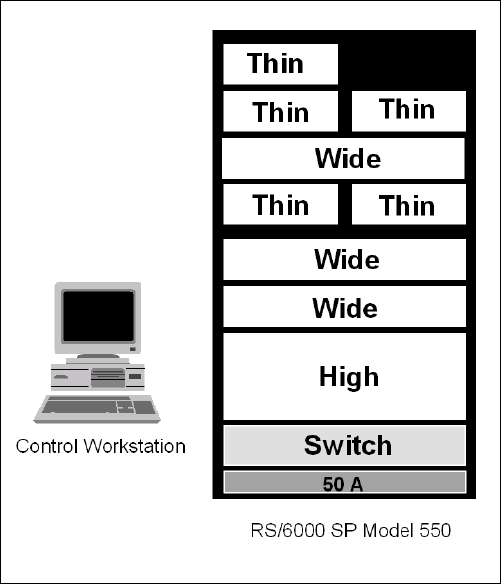

1.1.3 SP1® and early switch implementation

IBM in Yorktown, New York was working on a high-speed switch (6 MBps bandwidth and 200

ms latency) while another group on-site developed an eight-drawer frame and the associated

management software. In December 1991, these groups came together as HPSSL (the

“Development” part of the name was dropped) and were charged with shipping a product

within 12 months. Standard RS/6000 workstations were adapted, along with a new version of

the switch developed in Yorktown in place of ESCON for reduced latency. See Figure 1-3.

Figure 1-3 SP frame

The total product was introduced to the marketplace as the SP1 in September of 1993. By

year’s end, 72 systems had been installed around the world in the scientific and technical

community. As the mainframe began losing popularity, commercial customers also began

calling on IBM. IBM formed an application solutions group for the SP1, which, among other

things, ported a parallel version of Oracle’s database to the SP1.

1.1.4 PSSP and SP2®

In 1994, SP development absorbed personnel from the discontinued AIX/ESA® product.

They bolstered the manageability of the system and helped spawn the Parallel System

Support Programs (PSSP) software and the SP2 was born.

The Yorktown-developed switch gave way to the High Performance Switch (HiPS), running at

48 MBps bandwidth and 30 ms latency.

The SP2 moved out from under the umbrella of the Large Systems Division to become its

own enterprise within IBM. SP2 sales were strong: 352 systems were installed by the end of

1994 and 1,023 by the end of 1995.