10 IBM ^ xSeries 450 Planning and Installation Guide

1.3.3 EFI and legacy-free concept

The EFI complements legacy-free concept of PCs. Legacy-free refers to PC

system designs that eliminate certain hardware and firmware elements of the

original PC architecture while advancing the PC's stability and usability.

Specifically, we are talking about a set of I/O options that have been part of the

PC architecture for a very long time, for example parallel, serial and game port,

ISA slots or devices, floppy disk controller (FDC), PS/2® mouse, and keyboard.

BIOS interfaces require the OS loader to have a specific knowledge of the

workings of hardware devices. The EFI abstract concept makes it possible to

build code that works on a range of hardware devices without having explicit

knowledge of the specifics of these devices. This EFI feature allows a

replacement of legacy devices and adding new boot devices. The legacy devices

are replaced by USB devices in x450.

For more information about the EFI specification, see the following:

http://www.intel.com/technology/efi/index.htm

http://www.microsoft.com/hwdev/platform/firmware/EFI/default.asp

1.4 Intel Itanium 2 processor

The Itanium 2 processor used in the x450 (code named “Madison”) uses a ZIF

socket design, although the socket is designed differently from the one on the

x440, for example. This small form factor is what permits the x450 to have up to

four processors in a 4U node.

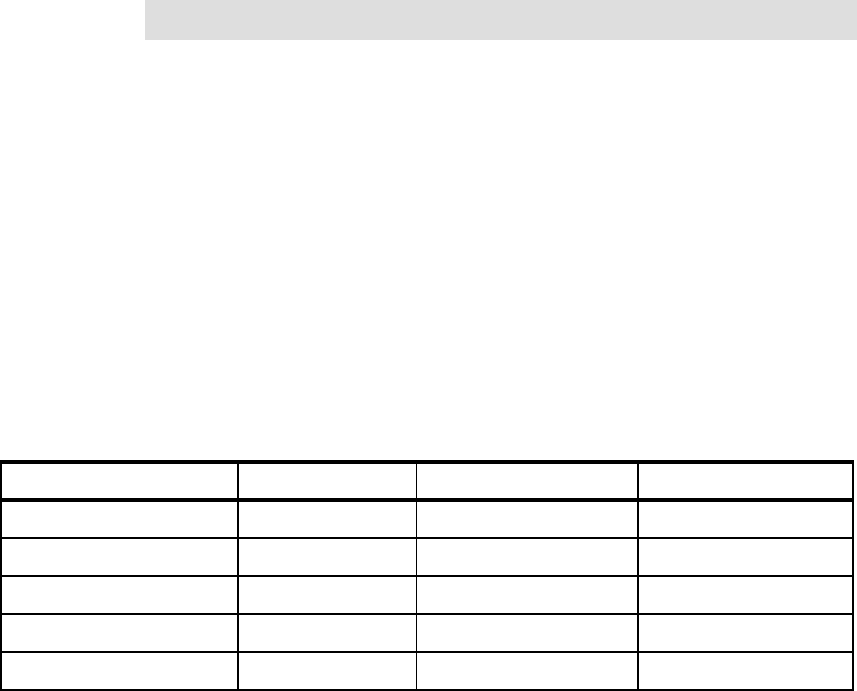

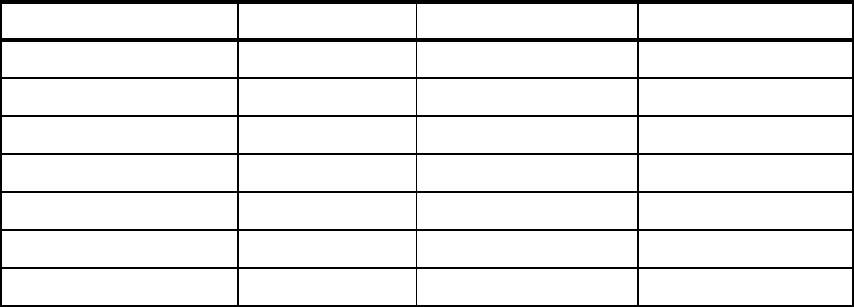

Table 1-3 outlines some of the differences between the Itanium and Itanium 2

processors (both the “Madison” and the earlier “McKinley” processor):

Table 1-3 Itanium vs Itanium 2 processors

Tip: One key interface that is no longer supported is INT 13, disk I/O.

Feature Itanium Itanium 2 “McKinley” Itanium 2 “Madison”

Processor core speed 733 or 800 MHz 900 MHz or 1.0 GHz 1.3, 1.4 or 1.5 GHz

L3 Cache 2 or 4 MB 1.5 or 3 MB 3, 4 or 6 MB

Frontside bus 266 MHz 400 MHz, 128 bit 400 MHz, 128 bit

Frontside bus bandwidth 2.1 GBps 6.4 GBps 6.4 GBps

Pipeline stages 10 8 8

Chapter 1. Technical description 11

The Itanium 2 processor has three levels of cache, all of which are on the

processor die:

Level 3 cache is equivalent to L2 cache on the Pentium III Xeon, or the L3

cache on the Pentium Xeon MP processor. Itanium 2 processors in the x450

models contain either 3, 4 or 6 MB of L3 cache. Unlike the design of the

original Itanium processor, this L3 cache is now on the processor die, greatly

improving performance, up or 2 times greater than that of the original Itanium.

Level 2 cache is equivalent to L1 cache on the Pentium III Xeon and is 256 KB

in size.

A new level 1 cache, 32 KB in size, is “closest” to the processor and is used to

store micro-operations (that is, decoded executable machine instructions) and

serves those to the processor at rated speed. This additional level of cache

saves decode time on cache hits.

The x450 also implements a Level 4 cache as described in 1.6, “IBM XceL4

Server Accelerator Cache” on page 17.

Intel has also introduced a number of features associated with its Itanium

micro-architecture. These are available in the x450, including:

400 MHz frontside bus

The Pentium III Xeon processor had a 100 MHz frontside bus that equated to

a burst throughput of 800 MBps. With protocols such as TCP/IP, this had been

shown to be a bottleneck in high-throughput situations. The Itanium 2

processor improves on this by using a single 200 MHz clock and using both

edges of each clock to transmit data. This is shown in Figure 1-6 on page 12.

Issue ports 9 11 11

on-board registers 328 328 328

Integer units 3 6 6

Branch units 3 3 3

Floating point units 2 2 2

SIMD units 2 1 1

Load and store units 2 (total) 2 load and 2 store 2 load and 2 store

Feature Itanium Itanium 2 “McKinley” Itanium 2 “Madison”

Get IBM eServer xSeries 450 Planning and Installation Guide now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.