Chapter 13

Spidergon: A NoC Modeling Paradigm

Chapter written by M. Copolla, R. LocateUi, G. Maruccia and L. Piéralisi,

STM, AST Grenoble Lab, France and

M. D. Grammatikakis, Computer Science Group, TEI-Crete, Heraklion, Crete, and

ISD Halandri, Greece.

13.1. Introduction

13.1.1. NoC: Communication Infrastructure for MPSoC

Software and hardware design for embedded applications in multiprocessor system-on-chip (MPSoC) is unable to cope with exponentially increasing mask costs and productivity requirements due to the escalating complexity and growing number of client services (see Figures 13.1-2). For example, the design of a recordable DVD (or hard disk drive) requires more than 100 person years, while a set-top box (or digital audio processing system) requires more than 1 million lines of code.

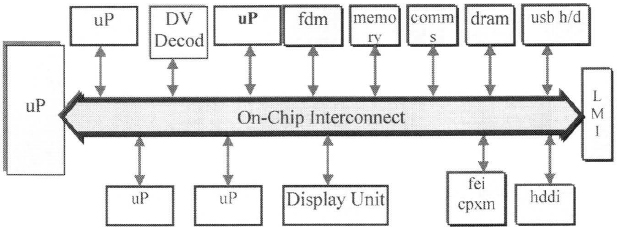

On-chip communication for MPSoC is currently realized using buses, such as AMBA [AMBA 04], STM's proprietary StBus, and IBM's Core-connect [IBM 04]. On-chip buses are designed and optimized to operate entirely within a single chip, thus wider buses are possible, and there is no constraint to the number of pins. These buses typically include address and data wires, bi-directional signaling for management, and complex arbitration. Bus implementation for future MPSoC containing billions of transistors on a single chip is increasingly hard. For example,

Figure 13.1. A typical complex multimedia ...

Get Model Driven Engineering for Distributed Real-Time Embedded Systems now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.