12.6. CPU Considerations

The challenge in building a large SMP is that because processors have increased performance through technology enhancements and the use of increasingly larger caches, the performance gains achieved through leveraging these caches are significant. Consequently, you need to cache relevant data whenever possible, to enable processors to have relevant data available and resident in their caches. Chip and hardware vendors have attempted to capitalize on this phenomenon through expansion of the processor and system cache.

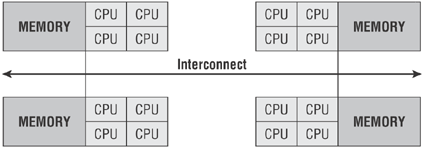

As a result, new system architectures such as cellular multiprocessing (CMP), CC-NUMA, shown in Figure 12-16, and NUMA (non-cache coherent) are now available in the market. Although this has been successful, it has produced two challenges: the need to manage data locally and cache coherency.

Figure 12-16. Figure 12-16

12.6.1. Data Locality

Data locality is the concept of having all relevant data locally available to the processor while it's processing a request. All memory within a system is available to any processor on any cell. This introduces the concepts of near memory and far memory. Near memory is the preferred method, as it is accessed by a processor on the same cell. As shown in Figure 12-17, accessing far memory is expensive because the request has to leave the cell and traverse the system interconnect crossbar to get the cell that ...

Get Professional Microsoft® SQL Server® 2008 Administration now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.