10.7 LOW-POWER IIR FILTER DESIGN USING PIPELINING AND PARALLEL PROCESSING

As illustrated in Chapter 3, pipelining and parallel processing can be used to reduce the power consumption of a system by reducing the supply voltage.

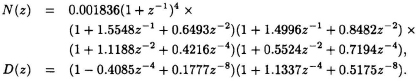

Example 10.7.1 Consider a low-power implementation of the following 4-th order Chebyshev low-pass filter [13]

![]()

Assume that the capacitance due to the multipliers is dominant and that the capacitance due to the adders can be neglected. Also, assume the supply voltage of the original system to be 5 V and the CMOS threshold voltage to be 1 V. By scattered look-ahead technique with power-of-2 decomposition, the 4-level pipelinable transfer function is given by N(z)/D(z) where

Power consumption can be reduced by using pipelining without altering the sample speed. Since the pipelined system has a shorter critical path than the original system, this smaller amount of charging capacitance can be charged or discharged during the same clock period as the original system. Therefore, the supply voltage of the pipelined system can be reduced to βV0, where β < 1 and V0 is the supply voltage of the original system. The propagation delay for the nonpipelined system is

![]()

For ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.