3

High-Speed Adder

3.1 CONDITIONAL-SUM ADDITION

In the study of ripple-carry adder we can see that carry propagation delay is the major concern when we try to speed up the addition of any two numbers. For an n-bit ripple-carry adder, the delay time is linear to n.

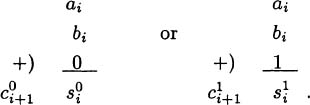

Notice that when adding two numbers as follows:

ci can be either 0 or 1 in binary. Only two cases are possible:

Here the superscript indicates the value of the carry-in assumed, and the subscript is for the bit index.

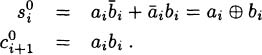

Under the assumption that the carry-in is 0, ![]() and

and ![]() can be easily found as follows:

can be easily found as follows:

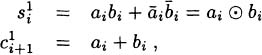

In a similar way, ![]() and

and ![]() can be found under the assumption that the carry-in is 1.

can be found under the assumption that the carry-in is 1.

where x y is .

Following the above logic, we build ...

Get Arithmetic and Logic in Computer Systems now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.