Event-Based Neuromorphic Systems

by Shih-Chii Liu, Tobi Delbruck, Giacomo Indiveri, Adrian Whatley, Rodney Douglas

13

Hardware Infrastructure

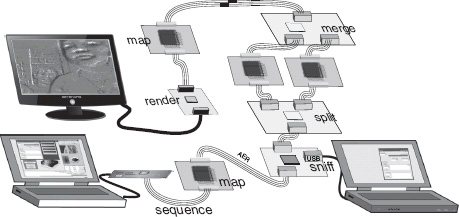

To make use of custom address event (AE) based neuromorphic chips built using the circuits described in the previous chapters, they need to be embedded into a larger hardware infrastructure. This chapter describes some of the considerations which must be borne in mind when designing, building, and operating the printed circuit boards which form this infrastructure for relatively small-scale, chiefly experimental systems. Examples are given taken from several projects. The necessary accompanying software is described in Chapter 14. The present chapter also includes a section reviewing the use of field programmable gate arrays (FPGAs) in neuromorphic systems. Hardware infrastructure for larger systems containing more than a handful of neuromorphic chips is discussed separately in Chapter 16.

13.1 Introduction

As we have already seen in Chapter 2, in order to construct larger AER systems, a certain amount of hardware infrastructure ‘glue’ is necessary between the active computational elements.

In fact even for the simplest systems, at least some means of capturing AE data is required. General purpose commercially available data acquisition boards are usually ill-suited to perform the asynchronous handshaking expected by an AER sender, and do not record the times at which individual events are received. For the purpose of capturing data from a simple experiment ...