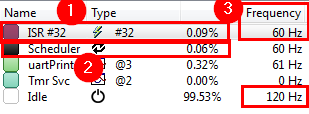

Let's take a look at the performance of the DMA-based implementation compared to the interrupt-driven approach:

This time around, we can make the following observations about the overall system behavior:

- The (DMA) ISR is now consuming < 0.1% of CPU cycles at 9,600 baud.

- The Scheduler CPU's consumption is still very low.

- The frequency of the ISR has been reduced to only 60 Hz (from 960 Hz). This is because, rather than creating an interrupt for every byte, there is only an interrupt generated at the end of the transfer of 16 bytes. The Idle task is being context-switched significantly less often as well. Although it seems ...