An Overview of the 386DX FSB

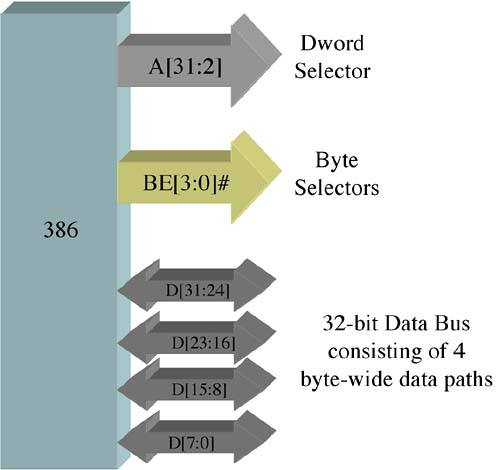

Figure 5-2 on page 44 illustrates the address- and data-related signals on the 386DX processor's FSB. Although the 386 processor implemented a full 32-bit internal address bus, the two least-significant address lines, A[1:0], were not implemented as output pins on the FSB.

Figure 5-2. 386DX FSB

Address Bus Selects Dword

Whenever the processor initiated a transaction on the FSB, logic external to the processor behaved as if the least-significant two address lines are always zero. As a result, the processor could only output addresses divisible by four. As an example, it could address location 00000100h, but not 00000101h, ...

Get The Unabridged Pentium 4 IA32 Processor Genealogy now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.