Request Phase Parity Checking

ChipSet Request Phase Parity Checking and Reporting

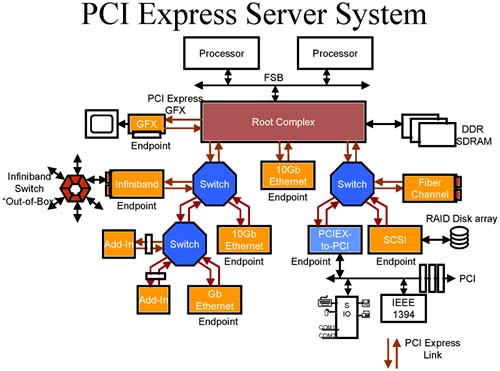

Refer to Figure 49-2 on page 1207. The example system shown is a PCI Express-based system and the device that connects the processors to the remainder of the system is referred to as the Root Complex. In a PCI or a PCI-X based system, it is referred to as the North Bridge or as the Memory Control Hub (MCH). The device that connects the processors to the remainder of the system is part of the chipset.

When a FSB agent other than the chipset (e.g., a processor) initiates a transaction on the FSB, the ...

Get The Unabridged Pentium 4 IA32 Processor Genealogy now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.