12

On-Chip AER Communication Circuits

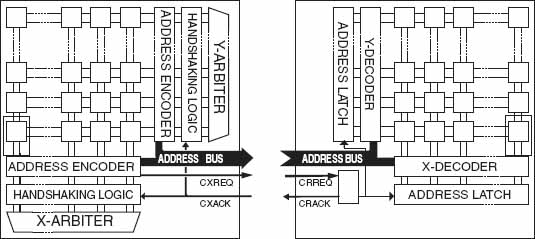

This chapter covers the on-chip transistor circuits used for the communication fabric introduced in Chapter 2; in particular the asynchronous communication circuits for receiving and transmitting address events following the Address Event Representation (AER) protocol. AER circuits are needed for transmitters that emit address events, for example the sensors described in Chapters 3 and 4 and the multineuron chips in Chapter 7. The receivers decode the incoming address events and stimulate the corresponding synapses and neurons on multineuron circuits as described in Chapters 7 and 8. They can also be stimulated by outputs of commodity digital chips or artificial spike trains played from the computer via interfaces of the kind described in Chapter 13.

12.1 Introduction

The circuits for the early neuromorphic chips were first designed by Sivilotti (1991) and Mahowald (1994), students at the time in Carver Mead’s laboratory at Caltech. These designs were influenced by the then on-going research in design of asynchronous circuits within the groups of Chuck Seitz and Alain Martin at Caltech. Designing asynchronous circuits was no easy matter at the time because design tools for asynchronous circuits were nonexistent. The Communicating Hardware Processes (CHP) design methodology introduced by Alain Martin, helped to facilitate the design of general ...

Get Event-Based Neuromorphic Systems now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.