PROBLEMS

8.1 Using only NAND gates, design a gated SR latch.

8.2 Using only NOR gates, design a gated D latch.

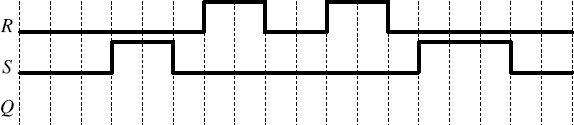

8.3 Determine the output Q of an SR latch for the input waveforms depicted in Figure P8.3. Assume that the output Q is reset initially.

Figure P8.3

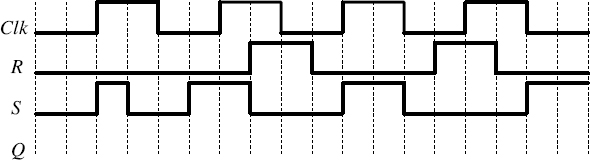

8.4 Determine the output Q of a gated SR latch for the input waveforms depicted in Figure P8.4. Assume that the output Q is reset initially.

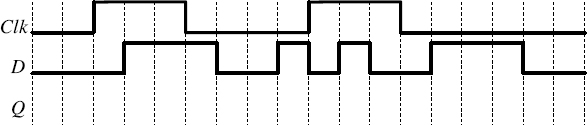

8.5 Determine the output Q of a gated D latch for the input waveforms depicted in Figure P8.5. Assume that the output Q is reset initially.

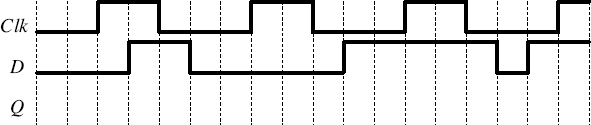

8.6 Determine the output Q of a gated D latch for the input waveforms depicted in Figure P8.6. Assume that the output Q is reset initially.

Figure P8.4

Figure P8.5

Figure P8.6

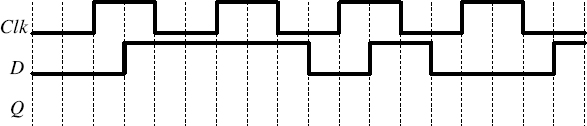

8.7 Determine the output Q of a gated D latch for the input waveforms depicted in Figure P8.7. Assume that the output Q is reset initially.

Figure P8.7

8.8 Determine the output Q of a positive edge-triggered D flip-flop for the input waveforms depicted in Figure P8.8. Assume that ...

Get Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.