Trio CoS Flow

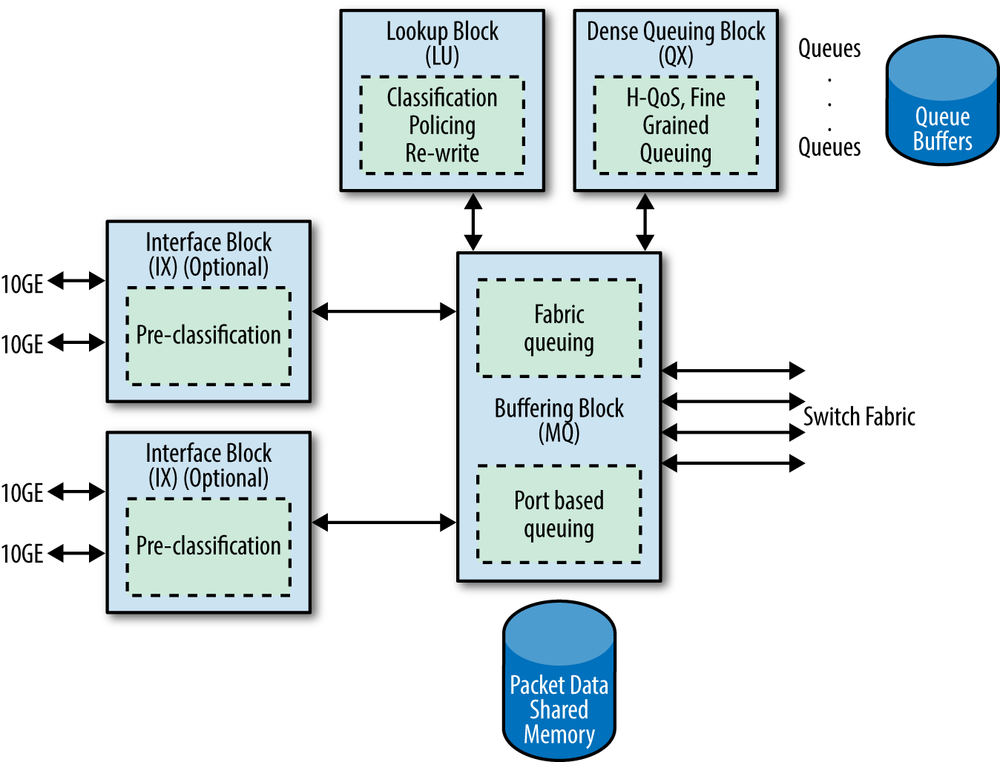

Note that general packet processing was detailed in Chapter 1. In this section, the focus is on the specific CoS processing steps as transit traffic makes its way through a MX router’s PFE complex. Figure 5-4 shows the major CoS processing blocks that might be present in a Trio PFE.

Figure 5-4. Trio PFE CoS Processing Points.

Note

The flexibility of the Trio chipset means that not all MPCs have all processing stages shown (most MPCs do not use the Interface Block/IX stage, for example, and in many cases a given function such as preclassification or shaping can be performed in more than one location). While the details of the figure may not hold true in all present or future cases Trio PFE cases, it does represent the how the Trio design was laid out with regards to CoS processing. Future versions of the Trio PFE may delegate functions differently and may use different ASIC names, etc. The names were exposed here to provide concrete examples based on currently shipping Trio chipsets.

Starting with ingress traffic at the upper left, the first processing stage is preclassification, a function that can be performed by the interface block (IX) when present or by the Buffering Block (MQ) on line cards that don’t use the IX.

Intelligent Oversubscription

The goal of preclassification is to prioritize network control traffic that is received over WAN ports (i.e., network ports, as ...

Get Juniper MX Series now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.