Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems

by Jean-Pierre Deschamps, Gery J.A. Bioul, Gustavo D. Sutter

11.2 INTEGERS

11.2.1 B's Complement Adders and Subtractors

The B's complement adder of Figure 11.46a is deduced from Algorithm 4.18. It consists of an (n + 1)-digit adder and two instances of the combinational circuit ext (digit extension) whose function is to represent x and y with an additional digit (sign digit):

![]()

Another circuit is shown in Figure 11.46b. Instead of generating an (n + 1)-digit output, this second adder generates an n-digit output and an overflow flag (Equation 4.17) is raised if the result cannot be expressed with n digits.

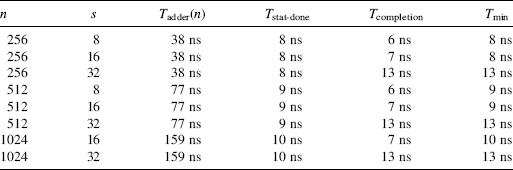

TABLE 11.4 Experimental Results

Figure 11.46 B's complement adders.

In order to synthesize a subtractor, or an adder-subtractor, another type of combinational circuit, namely, inv, is necessary. Given an n-digit number a, it computes

![]()

Two versions of a B's complement adder-subtractor are shown in Figure 11.47. The first one generates the exact (n + 1)-digit result. The other one generates an n-digit result and an overflow flag according to the relations (4.17) and (4.20). In both circuits the control signal defines the operation: addition (control ...