10.5 PARALLEL PROCESSING FOR IIR FILTERS

In this section, the techniques for parallel processing of IIR filters is discussed. Parallel processing for a simple 1st-order IIR filter is discussed first. After that, parallel processing for higher order filters is discussed.

Example 10.5.1 Consider the transfer function of a 1st-order IIR filter given in (10.49)

![]()

where ![]() for stability. This transfer function has only 1 pole located at z = a. The corresponding input output relation can be written as:

for stability. This transfer function has only 1 pole located at z = a. The corresponding input output relation can be written as:

![]()

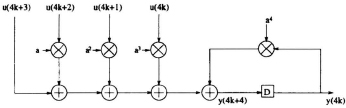

Consider the design of a 4-parallel architecture (L = 4) for the foregoing filter. Note that in the parallel system, each delay element is referred to as a block delay, where the clock period of the block system is 4 times the sample period. Therefore, instead of (10.50), the loop update equation should update y(n + 4) using inputs and y(n). By iterating the recursion (in (10.50)) or by applying

Fig. 10.14 Single state update operation in a 4-parallel filter.

look-ahead technique, we get

Substituting n = 4k in (10.51),

The corresponding architecture is shown in Fig. 10.14. Notice the ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.