14.4 HYBRID RADIX-4 ADDITION

In iterative or serial implementations of arithmetic operations, higher order radices can be employed to reduce the number of iteration cycles. Radix-4 is very appealing because it halves the number of iteration steps with regard to radix-2 and, in principle, is not much more complex to implement than radix-2.

This section considers the design of hybrid radix-4 addition. Designs of radix-4 architectures for subtraction or addition/subtraction are left as exercises to the reader. Radix-4 redundant signed-digit sets can be maximally redundant based on digit set D<4.3> or minimally redundant based on digit set D<4.2>.

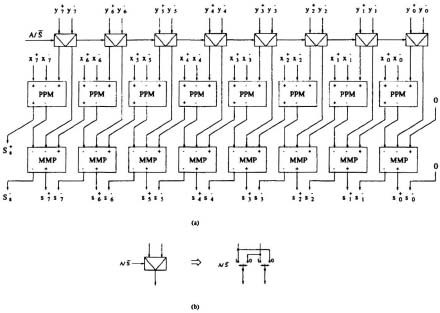

Fig. 14.5 (a) Signed binary digit adder/subtractor. (b) Definition of the switching box.

Fig. 14.6 Digit-serial SBD redundant adders. (a) Lsd-first adder; (b) msd-first adder.

14.4.1 Maximally Redundant Hybrid Radix-4 Addition

Hybrid radix-4 addition can be carried out in a way similar to the hybrid radix-2 addition. Table 14.4 summarizes the digit sets used in maximally redundant hybrid radix-4 addition (MRHY4A) S<4.3> = X<4.3> + Y4. The last column of the table lists the binary codes assigned to the digits. Notice that the binary codes of the digits xi and si ∈ D<4.3>, and yi ∈ D4, correspond to the weighted addition of 2 consecutive ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.