3.3 PARALLEL PROCESSING

It is of interest to note that parallel processing and pipelining techniques are duals of each other, and if a computation can be pipelined, it can also be processed in parallel. Both techniques exploit concurrency available in the computation in different ways. While independent sets of computations are computed in an interleaved manner in a pipelined system, they are computed using duplicate hardware in parallel processing mode.

3.3.1 Designing a Parallel FIR System

Consider the 3-tap FIR filter described by (3.1). This system is a single-input single-output (SISO) system and is described by

![]()

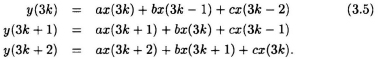

To obtain a parallel processing structure, the SISO system must be converted into a MIMO (multiple-input multiple-output) system. For example, the following set of equations describe a parallel system with 3 inputs per clock cycle (i.e., level of parallel processing L = 3).

Here k denotes the clock cycle. As can be seen, at the k-th clock cycle the 3 inputs x(3k), x(3k + 1) and x(3k + 2) are processed and 3 samples are generated at the output. Parallel processing systems are also referred to as block processing systems and the number of inputs processed in a clock cycle is referred to as the block size. Because of the MIMO structure, placing a latch at any line ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.