3.6 PROBLEMS

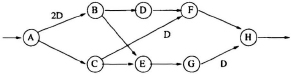

- Consider the DFG shown in Fig. 3.20. Assume the time required for each operation is T.

Fig. 3.20 Data-flow graph for Problem 1.

(a) What is the maximum achievable sample rate in this system?

(b) Place pipelining registers at appropriate feed-forward cutsets such that the sample rate of this system can be approximately equal to 1/T. Clearly identify the feed-forward cutsets and count the total number of pipelining registers required.

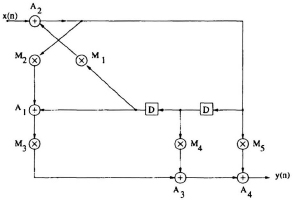

- Consider the IIR digital filter block diagram shown in Fig. 3.21. Assume that the multiplication operation takes 2 u.t. and the addition operation takes 1 u.t.

Fig. 3.21 Digital IIR filter for Problem 2.

(a) Calculate the critical path of the IIR filter.

(b) Pipeline the IIR filter by placing latches at appropriate feed-forward cutsets to reduce the critical path to 3 u.t.

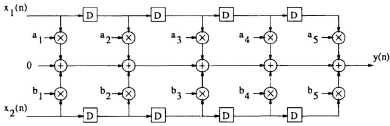

- Consider the nonrecursive signal processing structure shown in Fig. 3.22. Find an equivalent data-broadcast implementation of this algorithm to

Fig. 3.22 Data-flow graph for Problem 3.

improve the speed of the system. Do not use any additional latches. Calculate the throughput or sample speed of the broadcast architecture. (Hint: Transpose operation is ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.