16.6 MULTIPLIER

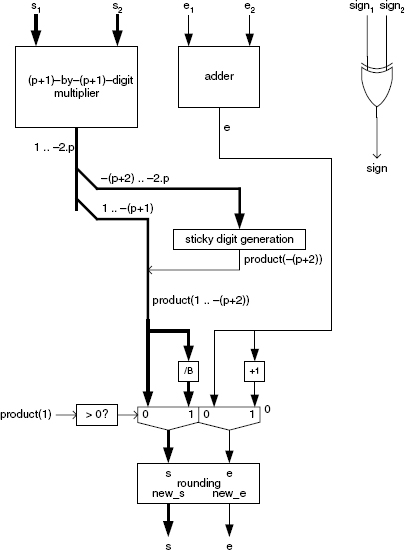

A basic multiplier deduced from Algorithm 16.5 is shown in Figure 16.6. The rounding circuit is the same as in the case of the adder-subtractor (Figure 16.4).

Figure 16.6 Multiplier.

Example 16.8 (Complete VHDL code available.) Generate the VHDL model of a generic floating-point multiplier. It is made up of four blocks:

1. Multiplication. The multiplication circuit corresponds to a (p + 1)-by-(p + 1) multiplier, an adder and a XOR gate—Figure 16.6—and generates the exact value of the product. Any type of multiplier can be used (Chapter 12). In this model, a simple parallel multiplier has been used:

entity multiplication is port ( s1, s2: in digit_vector(0 downto -p); sign1, sign2: in std_logic; e1, e2: in integer; s: out digit_vector(1 downto -2*p); sign: out std_logic; e: out integer ); end multiplication; architecture circuit of multiplication is component basic_base_B_mult…end component; … end circuit;

2. Generation of the guard digits. This block computes the sticky digit and concatenates its value with positions 1 down to – (p + 1) of the exact product:

entity guard_digits is port ( s: in digit_vector(1 downto -2*p); product: out digit_vector(1 downto -(p+2)) ); end guard_digits; architecture behavior of guard_digits is begin process(s) variable acc_or: digit; begin acc_or:=0; for i in -(p+2) downto -2*p loop if (s(i)>0) or (acc_or>0) then acc_or:=1; end ...

Get Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.