E.2 MULTIPLEXER-BASED FAST BINARY ADDERS

This section considers implementation of Manchester, carry-select, and carry- look-ahead based fast binary adders using multiplexers only.

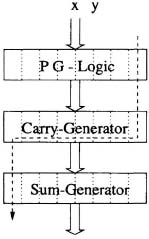

Fig. E.1 Block diagram of a Manchester adder.

E.2.1 Multiplexer-Based Manchester Adder

In a binary addition, a carry ci can be either generated at stage i or propagated from the preceding stage. A carry is generated at stage i if xi and yi are both 1, and a carry is propagated from stage i−1 to stage i+1 if only one of the operands (xi, yi) is 1 but not both [1]. Let gi and pi denote the carry generation and the propagation at stage i. These can be computed as:

![]()

![]()

where ⊕ denotes XOR operation. The carry ci+1 and the sum si at each stage are computed by:

![]()

![]()

Hence, an adder based on this principle consists of 3 sequential stages:

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.