April 2015

Intermediate to advanced

584 pages

21h 24m

English

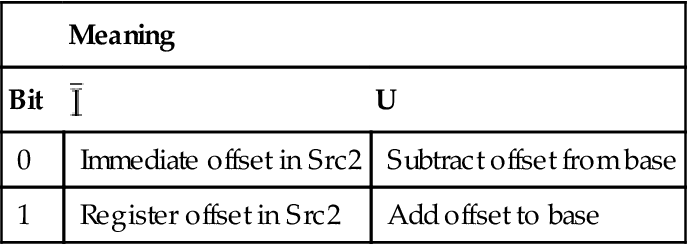

Table 6.10

Index mode control bits for memory instructions

| P | W | Index Mode |

| 0 | 0 | Post-index |

| 0 | 1 | Not supported |

| 1 | 0 | Offset |

| 1 | 1 | Pre-index |

Table 6.11

Memory operation type control bits for memory instructions

| L | B | Instruction |

| 0 | 0 | STR |

| 0 | 1 | STRB |

| 1 | 0 | LDR |

| 1 | 1 | LDRB |