Segmentation in Hardware

Starting with the 80286 model, Intel microprocessors perform address translation in two different ways called real mode and protected mode . We’ll focus in the next sections on address translation when protected mode is enabled. Real mode exists mostly to maintain processor compatibility with older models and to allow the operating system to bootstrap (see Appendix A for a short description of real mode).

Segment Selectors and Segmentation Registers

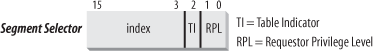

A logical address consists of two parts: a segment identifier and an offset that specifies the relative address within the segment. The segment identifier is a 16-bit field called the Segment Selector (see Figure 2-2), while the offset is a 32-bit field. We’ll describe the fields of Segment Selectors in the section "Fast Access to Segment Descriptors" later in this chapter.

Figure 2-2. Segment Selector format

To make it easy to retrieve segment selectors quickly, the processor provides segmentation

registers whose only purpose is to hold Segment Selectors; these

registers are called cs, ss, ds,

es, fs, and gs. Although there are only six of them, a

program can reuse the same segmentation register for different

purposes by saving its content in memory and then restoring it

later.

Three of the six segmentation registers have specific purposes:

csThe code segment register, which points to a segment containing program ...

Get Understanding the Linux Kernel, 3rd Edition now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.