Appendix C: Tutorial on the Use of Verilog HDL to Simulate a Finite-State Machine Design

C.1 INTRODUCTION

This appendix quickly describes an FSM model in Verilog code and then simulates it using SynaptiCAD's VeriLogger Extreme simulator. The code for the model, VeriLogger Extreme, and the code for most of the examples in the book are contained on the CDROM provided with the book.

A more detailed account of the Verilog HDL is provided in Chapters 6–8, where the language is developed at a slower and more defined pace.

C.2 THE SINGLE PULSE WITH MEMORY SYNCHRONOUS FINITE-STATE MACHINE DESIGN: USING VERILOG HDL TO SIMULATE

The design of a single-pulse generator with memory is outlined and then a Verilog HDL file is created. This Verilog file will use the most basic of the Verilog methods so as to keep it simple.

C.2.1 Specification

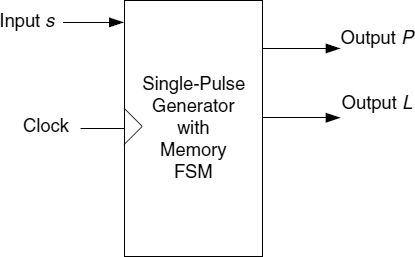

Whenever input s is asserted high, a single pulse is to be generated at the output P. Signal s must be returned low and then reasserted high again before another pulse can be generated. In addition, a memory output L is to go high to indicate that a pulse has been generated; going low again when the s input is returned to logic 0.

C.2.2 Block Diagram

Figure C.1 illustrates the block diagram of the system.

Figure C.1 Block diagram of the system.

C.2.3 State Diagram

A state diagram is implemented as illustrated in Figure C.2.

C.2.4 Equations from the State Diagram ...

Get FSM-based Digital Design using Verilog HDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.