9.2. TRANSACTION FLOW

In considering the mapping of the PCI bus to RapidIO it is important to understand the transaction flow of PCI transactions through RapidIO.

9.2.1. PCI 2.2 to RapidIO Transaction Flow

9.2.1.1. Posted PCI to RapidIO Transaction

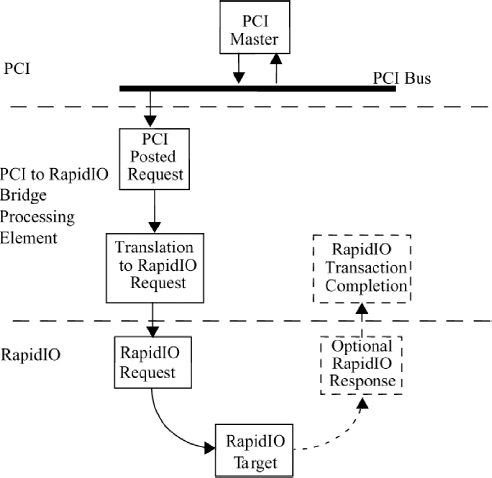

The PCI 2.2 specification defines two classes of transaction types, posted and non-posted. Figure 9.4 shows the route taken by a PCI to RapidIO posted write transaction. Once the request is sent from the PCI master on the bus, it is claimed by the bridge processing element which uses the AMT to translate it into a RapidIO request. Only when the transaction is in RapidIO format can it be posted to the RapidIO target. In some cases it may be desirable to guarantee end-to-end delivery of the posted write transaction. For this case the RapidIO NWRITE_R transaction is used which results in a response as shown in the figure.

Figure 9.4. PCI mastered posted write transaction flow diagram

9.2.1.2. Non-posted PCI to RapidIO Transaction

A non-posted PCI transaction is shown in Figure 9.5. The transaction is mastered by the PCI agent on the PCI bus and accepted by the RapidIO to PCI bridge. The transaction is retried on the PCI bus if the bridge is unable to complete it within the required time-out period. In this case the transaction is completed as a delayed transaction. The transaction is translated to the appropriate RapidIO operation ...

Get RapidIO: The Next Generation Communication Fabric For Embedded Application now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.