4.6 PROBLEMS

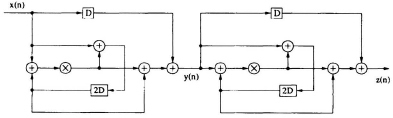

- Consider the wave digital filter shown in Fig. 4.15. Assume that each multiply operation requires 20 nsec and each add operation requires 8 nsec.

Fig. 4.15 The wave digital filter structure in Problem 1.

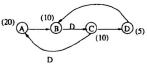

Fig. 4.16 Data-flow graph for Problem 2.

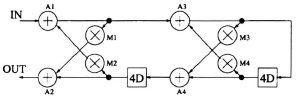

Fig. 4.17 A 4-level pipelined all-pass 8th-order IIR digital filter.

(a) Calculate the iteration period bound of this filter by inspection.

(b) What is the critical path?

(c) Manually pipeline and/or retime this filter to achieve a critical path equal to the iteration period bound.

- Consider the DFG shown in Fig. 4.16, where the number at each node denotes its execution time.

(a) What is the maximum sample rate of this DFG?

(b) What is the fundamental limit on the sample period for the system described by this DFG?

(c) Manually retime this DFG to minimize the clock period.

- Consider the 4-level pipelined all-pass 8th-order IIR digital filter DFG in Fig. 4.17. Assume that addition and multiplication require 1 and 2 u.t., respectively.

(a) By inspection, calculate the iteration bound.

(b) Compute the critical path time of the circuit.

(c) Pipeline and/or retime this system to achieve a critical path of 2 u.t. ...

Get VLSI Digital Signal Processing Systems: Design and Implementation now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.